## CSC 343 LAB

## 32\*8 SRAM design

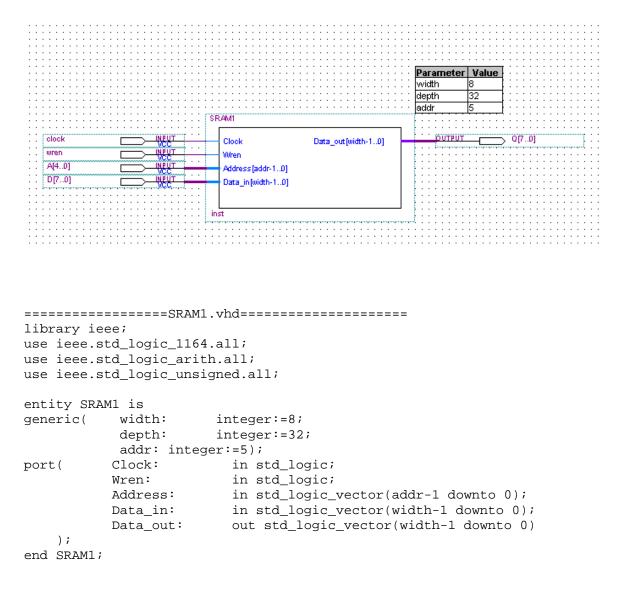

This is a 32\*8 RAM(sram1.vhd). It contains 32 eight-bit words, which are accessed using a five-bit address port(A[4..0]), a eight-bit data input port(D[7..0]), a eight-bit date output port(Q[7..0]), a write/Read control input(wren), and a clock.

When wren is low and clock comes (positive trigger), data from D will be stored into the memory with the corresponding address. When wren is high and clock comes, data will be read from the memory with the corresponding address into port Q.

architecture behav of SRAM1 is

```

type ram_type is array (0 to depth-1) of

std_logic_vector(width-1 downto 0);

signal tmp_ram: ram_type;

begin

process(Clock, Wren)

begin

if (Clock'event and Clock='1') then

if Wren='1' then

-- buildin function conv_integer change the type

-- from std_logic_vector to integer

Data_out <= tmp_ram(conv_integer(Address));</pre>

elsif Wren='0' then

tmp_ram(conv_integer(Address)) <= Data_in;</pre>

Data_out <= (Data_out'range => 'Z');

end if;

end if;

end process;

end behav;

```

## The output of 32\*8 SRAM:

| Simulation Waveforms    |               |                            |              |                         |      |                      |                   |          |      |

|-------------------------|---------------|----------------------------|--------------|-------------------------|------|----------------------|-------------------|----------|------|

| Simulation mode: Timing |               |                            |              |                         |      |                      |                   |          |      |

|                         |               |                            |              |                         |      |                      |                   |          |      |

|                         |               |                            |              |                         |      |                      |                   |          |      |

| Mast                    | ter Time Bar: | 11.725 ns                  | • • Pointer: | 33.72 n                 | s    | Interval:            | 22.0 ns           | Start:   |      |

|                         |               | Value a Oips               |              | 160 <sub>,</sub> 0 ns   |      | 320 <sub>,</sub> 0 r | IS                | 480,0 n  | IS   |

|                         | Name          | Value a<br>11.73 r<br>11.7 | 25 ns        |                         |      |                      |                   |          |      |

|                         | clock         | во                         |              |                         |      |                      |                   |          |      |

|                         | wren          | во                         |              |                         |      |                      |                   |          |      |

| i 💕                     | ΞA            | н от 🚺 От                  | X 02 X       | 03 <u>X</u> 04 <u>X</u> | 05 X | 01 X 02              | χ 03 χ 04         | <u> </u> | 06   |

| D)                      | 🛨 D           | наа 🚺 🗛                    | X AB X       | AC X AD X               | AE X | AF X BO              | <u>χ B1 χ B</u> 2 | : Х ВЗ Х | B4   |

| $\bigcirc$              | 🛨 Q           | н 🗠 🚺                      |              | ZZ                      |      | X AA X               | AB 🗶 AC           | X AD X   | AE ) |

|                         |               |                            |              |                         |      |                      |                   |          |      |

|                         |               |                            |              |                         |      |                      |                   |          |      |

|                         |               |                            |              |                         |      |                      |                   |          |      |

|                         |               |                            |              |                         |      |                      |                   |          |      |

|                         |               |                            |              |                         |      |                      |                   |          |      |

|                         |               |                            |              |                         |      |                      |                   |          |      |

|                         |               |                            |              |                         |      |                      |                   |          |      |

|                         |               |                            |              |                         |      |                      |                   |          |      |